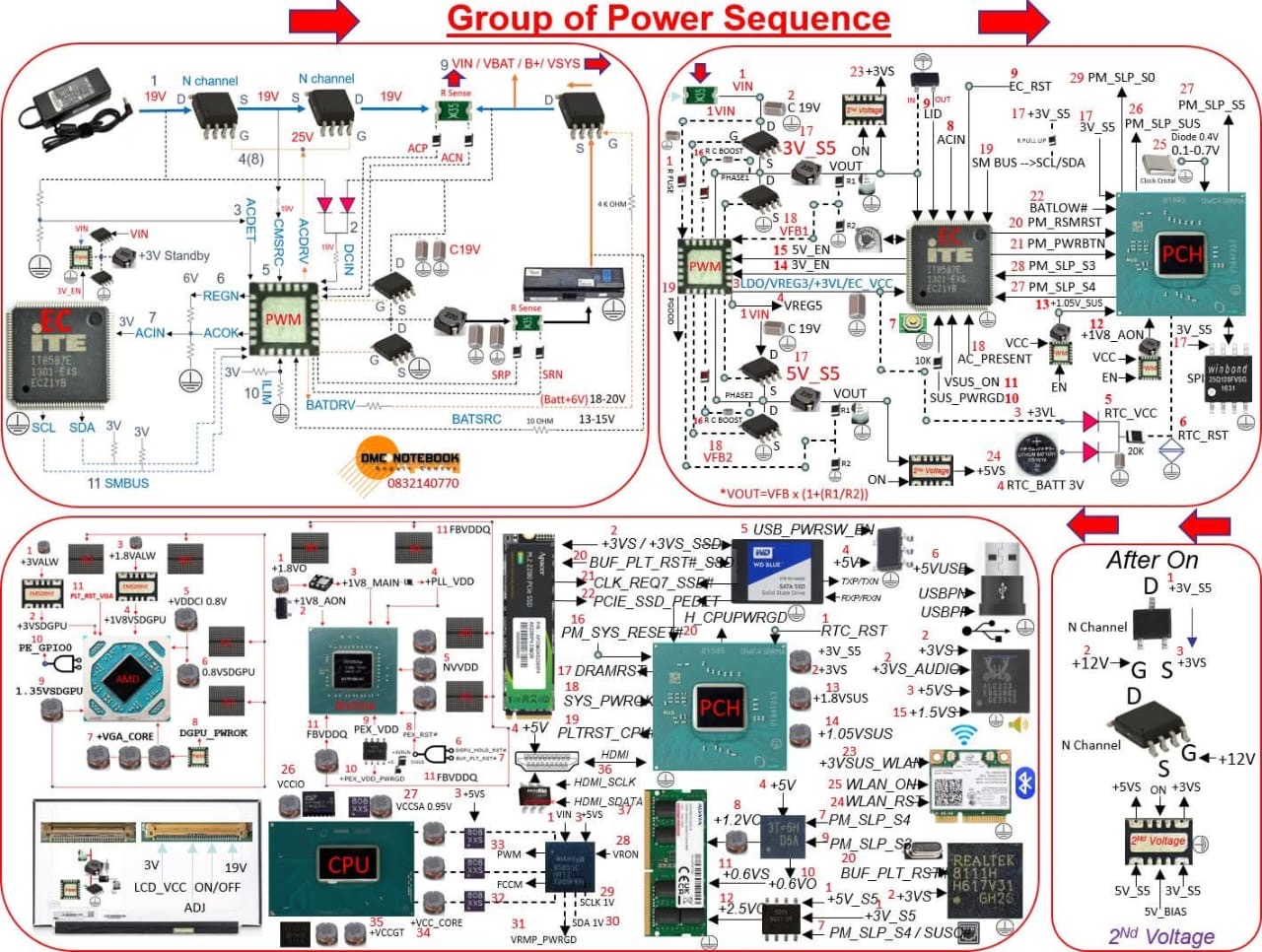

LAPTOP POWER SEQUENCE Step by step

CLICK ON IMAGE LAPTOP POWER SEQUENCE STEP BY STEP LAPTOP POWER SEQUENCE EXPLAIN IN IMAGE.

This is the complete laptop motherboard sequence from:

Adapter → EC → +3V/+5V → PCH → CPU → RAM → Devices

✅ FULL POWER SEQUENCE + SIGNAL LIST (Single Master Table)

Step | Stage | Signal / Rail Name (From Image) | Expected Value | Generated By → Goes To | Measurement Point |

|---|---|---|---|---|---|

1 | Adapter Input | DCIN / VIN | +19V | Adapter → Charger MOSFET | DC Jack Pin |

2 | Adapter MOSFET ON | B+ / VSYS / VBAT | +19V | Charger → System Rail | After DC MOSFET |

3 | Charger Detect | ACIN | 3.3V | Charger → EC | EC ACIN Pin |

4 | Adapter OK | ACOK# | 3.3V High | Charger → EC | EC Input Pin |

5 | EC Power Start | +3V Standby / +3VALW | +3.3V Always | PWM → EC_VCC | Coil near EC |

6 | EC Alive Rail | EC_VCC | +3.3V | +3VALW → EC | EC Supply Pin |

7 | SMBUS Active | SCL / SDA (SMBUS) | 3.3V Pulsing | EC ↔ Charger/PCH | BIOS/EC Lines |

8 | Enable Suspend Rails | 3V_EN | 3.3V | EC → PWM Controller | Enable Pin |

9 | Enable Suspend Rails | 5V_EN | 3.3V | EC → PWM Controller | Enable Pin |

10 | Suspend Rail Output | +3V_S5 / +3VSUS | +3.3V | PWM → PCH/BIOS | SUS Coil |

11 | Suspend Rail Output | +5V_S5 / +5VSUS | +5V | PWM → USB/Audio | SUS Coil |

12 | Suspend Power Good | SUS_PWRGD | High (3.3V) | EC → PCH | Signal Test Pad |

13 | PCH Reset Output | PM_RSMRST# | High | PCH → System | Near PCH Pin |

14 | EC Reset | EC_RST | High | EC → System Reset | EC Pin |

15 | Sleep Exit S5 | PM_SLP_S5# | High | PCH → Regulators | PCH Pin |

16 | Sleep Exit S4 | PM_SLP_S4# | High | PCH → Devices | PCH Pin |

17 | Sleep Exit S3 | PM_SLP_S3# | High | PCH → Devices | PCH Pin |

18 | Sleep Exit S0 | PM_SLP_S0# | High | PCH → Full ON Rails | PCH Pin |

19 | Always RTC Rail | RTC_BATT (3V) | +3V | CMOS Battery → RTC | RTC Cell Pin |

20 | RTC Supply | RTC_VCC | +3.3V | +3VALW → RTC | RTC Coil |

21 | RTC Reset Signal | RTC_RST | High | EC/PCH → RTC | BIOS Area |

22 | BIOS Power | SPI VCC (Winbond) | +3.3V | +3VSUS → BIOS | BIOS Pin 8 |

23 | BIOS Communication | SPI_CLK / MOSI / MISO / CS# | Pulsing | PCH ↔ BIOS | BIOS Pins |

24 | PCH Core Rail | +1.05VSUS | +1.05V | Regulator → PCH | PCH Coil |

25 | PCH Logic Rail | +1.8VSUS | +1.8V | Regulator → PCH | Coil Near PCH |

26 | Main Power Enable | VSUS_ON | High | EC → Main Rails | EC Output |

27 | Power Button Signal | PWRBTN# | Low Pulse | EC → PCH | Button Line |

28 | CPU VR Enable | VRON | High | PCH → CPU VRM | VRM Controller Pin |

29 | CPU Core Voltage | VCC_CORE / VCORE | 0.7–1.2V | VRM → CPU | CPU Coil |

30 | CPU Power Good | VRMPWRGD | High | VRM → PCH | VRM Signal Pin |

31 | DDR Rail Output | +1.2V / +1.35V DDR | 1.2–1.35V | Regulator → RAM | RAM Coil |

32 | RAM Reset Signal | DRAMRST# | High | PCH → RAM | Near RAM Slot |

33 | System Reset Output | PM_SYS_RESET# | High | PCH → System | PCH Pin |

34 | System Power Good | SYS_PWRGD | High | PCH → All Devices | Test Pad |

35 | SSD Power Rail | +3VS / +3VS_SSD | +3.3V | Regulator → SSD | SSD Coil |

36 | PCIe Clock Request | CLK_REQ# | Pulsing | SSD/WLAN → PCH | PCIe Line |

37 | WLAN Power Rail | +3VSUS_WLAN | +3.3V | SUS Rail → WLAN | WLAN Coil |

38 | WLAN Reset | WLAN_RST# | High | PCH → WLAN | WLAN Pin |

39 | USB Rail | +5VUSB | +5V | +5VSUS → USB Port | USB Fuse |

40 | Audio Rail | +3VS_AUDIO | +3.3V | SUS Rail → Audio Codec | Audio Coil |

41 | LCD Main Rail | LCD_VCC | +19V | B+ → LCD Circuit | LCD Connector |

42 | Backlight Enable | BL_ON | High | EC → LCD Driver | LCD Signal Pin |

43 | dGPU Power Rail | +1.8VSDGPU / +VCORE_DGPU | 0.8–1.8V | VRM → GPU | GPU Coil |

44 | dGPU Power OK | DGPU_PWR_OK | High | GPU VRM → PCH | GPU Signal |

45 | Final State | System Fully ON (S0) | All Stable | CPU+PCH+RAM Active | Board Running |

✅ COMPLETE POWER SEQUENCE FLOW (One Line)

19V → ACOK/ACIN → +3VALW → EC Alive →

3V_EN/5V_EN → +3VSUS/+5VSUS →

SUS_PWRGD → PM_RSMRST →

PM_SLP_S5/S3/S0 →

VRON → VCORE →

DRAMRST → SYS_PWRGD →

USB/WLAN/LCD/GPU ON